An International Open Access, Peer-Reviewed Refereed Journal Impact Factor: 6.4 Website: <a href="https://ijarmt.com">https://ijarmt.com</a> ISSN No.: 3048-9458

## Finite Impulse Response using Different Multiplier and Adder: A Study

### Naman Gupta

M. Tech. Scholar, Department of Electronics and Communication Engineering, TCST,

Bhopal

## Prof. Abhishek Agwekar

Head of Dept., Department of Electronics and Communication Engineering, TCST, Bhopal

Shivam Gupta

Technical Leader, KPIT Technologies Limited

#### **Abstract**

The most important criteria for the design and implementation of DSP processor are area optimization and reduction in power consumption. The fundamental block for the design and implementation of the DSP processor is the Finite Impulse Response Filter. The Finite Impulse Response (FIR) Filter consists of three basic modules which are adder blocks, flip flops and multiplier blocks. The performance of the FIR Filter is largely influenced by the multiplier, which is the slowest block out of all. The multiplier, the slowest block of all, has a significant impact on the FIR Filter's performance.

Booth's multiplication algorithm is an algorithm which multiplies two signed binary numbers in two's complement notation. Booth's algorithm is of interest in the study of computer architecture. It can be used for both signed-magnitude numbers as well as 2's complement numbers with no need for a correction term or a correction step. In this paper the studied of different types of adder and booth multiplier is present.

Keywords: - Booth Multiplier, Different Types of Adder, Finite Impulse Response

### **INTRODUCTION**

Digital Signal Processing (DSP) plays a vital role in modern electronics, with applications ranging from communication systems and audio processing to image enhancement and biomedical engineering. Among various signal processing operations, filtering is a fundamental task, and Finite Impulse Response (FIR) filters are one of the most widely used types due to their inherent stability and linear phase response. FIR filters are non-recursive digital filters whose output depends only on the current and previous input values, making them ideal for a wide range of real-time applications [1, 2].

An International Open Access, Peer-Reviewed Refereed Journal Impact Factor: 6.4 Website: <a href="https://ijarmt.com">https://ijarmt.com</a> ISSN No.: 3048-9458

The performance of an FIR filter is significantly influenced by the efficiency of the underlying arithmetic operations, especially multiplication and addition. In typical FIR filter implementations, a large number of multiply-and-accumulate (MAC) operations are required. As the filter order increases, the computational complexity and hardware resource requirements also increase. Therefore, selecting the right multiplier and adder architecture becomes critical in optimizing the filter for area, speed, and power consumption [3].

Multipliers such as Booth, Wallace Tree, and Vedic have different characteristics in terms of speed, power efficiency, and hardware complexity. Booth multipliers reduce the number of partial products but introduce sequential complexity. Wallace Tree multipliers are fast due to their parallelism, but they consume more area. Vedic multipliers is based on ancient Indian mathematics, offer high speed and compact design, making them suitable for low-power and high-performance applications.

Similarly, adders like Ripple Carry Adder (RCA), Carry Look-Ahead Adder (CLA), and Carry Save Adder (CSA) also influence the speed and power of FIR filters. RCA is simple but slow, CLA improves speed with increased logic, and CSA provides fast accumulation by avoiding carry propagation delays during intermediate steps [4].

This study focuses on designing and analyzing FIR filters using different combinations of these multipliers and adders. The goal is to identify the most optimal arithmetic unit combination that enhances the overall performance of the FIR filter, especially for VLSI and FPGA-based systems. The filter is modeled in Verilog HDL and synthesized using standard FPGA tools to evaluate performance metrics such as area (in terms of logic utilization), delay (propagation time), and power consumption.

The changed Booth calculation is widely utilized for fast multiplier circuits. Once, when exhibit multipliers were utilized, the diminished number of created fractional items altogether improved multiplier execution. In structures dependent on decrease trees with logarithmic rationale profundity, be that as it may, the diminished number of halfway items limitedly affects generally speaking execution. The Baugh-Wooley calculation [5] is an alternate plan for marked increase, however isn't so broadly received in light of the fact that it might be confounded to send on sporadic decrease trees. Again the Baugh-Wooley calculation is for just marked number increase. The exhibit multipliers [6] and Braun cluster multipliers [7] works just on the unsigned numbers. In this manner, the necessity of the cutting edge PC framework is a committed and extremely rapid multiplier unit that can perform increase task on marked

An International Open Access, Peer-Reviewed Refereed Journal Impact Factor: 6.4 Website: <a href="https://ijarmt.com">https://ijarmt.com</a> ISSN No.: 3048-9458

just as unsigned numbers. In this paper we structured and executed a devoted multiplier unit that can perform augmentation task on both marked and unsigned numbers, and this multiplier is called as SUMBE multiplier.

### LITERATURE REVIEW

**K. Sravani et al. [1].** in a finite impulse response filter (FIR), the impulse response has a finite period. To attain exact frequency specifications in a variety of digital signal processing applications, a higher order FIR filter is required. On the other hand, the number of multipliers and adders increases linearly with the length of the leading filter. The fundamental building blocks for the development and use of the FIR filter are the multiplier, adder, and flip flop blocks. The performance of the FIR filter is greatly influenced by the multiplier, the slowest block in the adder. The delay will be decreased by using the Booth Multiplier and carry select adder in the Finite Impulse Response Filter. A number of parameters have been compared between the filter and other filters. The suggested lowpass filter is a 15-tap filter that was designed using Verilog HDL and implemented using Xilinx 14.7 Vivado tools. Both the area and the latency have been decreased. The booth multiplier is a great option for creating FIR filters for low voltage and low power VLSI applications because it also reduces latency, power consumption, and operating frequency.

A. S. Kumar et al. [2], every day, people utilize cars, and technological improvements in them have been happening at a rapid pace. In this study, we built a robot car that is easily controlled by a mobile device. AVR Studio and Android Studio are used to create a basic application that allows a robot to move and be controlled remotely via a Bluetooth module. An Atmega8 microcontroller is utilized to control the entire system. The robotic system uses the infrared sensors to identify impediments in its route. The Atmega8 microcontroller interfaces with modules like motors, Bluetooth, and infrared sensors. The AVR studio is used to program the controller. It is expected that this research would act as a roadmap for the creation of future technical innovations.

A. S. Kumar et al. [3], an FPGA is an integrated circuit that is created by a designer and set up using a language that describes the hardware. Therefore, we can use RRAM to store the data on FPGA by adding some memory. Routing multiplexers based on Resistive Random-Access Memory improve the features of FPGA design. When compared to SRAM implementations, the circuit design features of RRAM-based multiplexers can be distinguished by their delay parameters with changes in input size since they regulate the set or reset operation, making

An International Open Access, Peer-Reviewed Refereed Journal Impact Factor: 6.4 Website: <a href="https://ijarmt.com">https://ijarmt.com</a> ISSN No.: 3048-9458

them electrical parameters. Circuit optimization is the suggested approach. We employed tiny programming transistors in 1-Transistor 1-Ram based multiplexers, and the one-level RRAM-based multiplexers vary according to the size of the input. For the best product delay power, programming transistors are typically tiny in size. Additionally, RRAM multiplexers require a reduced footprint; the suggested architecture for the routing tracks must redefine the routing tracks, and the area reduction might be more sufficiently large. We examined the power consumption and optimization of RRAM and SRAM-based FPGA architectures in this work, and the results were better than those of our suggested RRAM approach.

B. N. K. Reddy et al. [4], in the field of multiprocessors, Network-on-Chip is a new paradigm that was developed by creating interconnected patterns. Because of the advanced routing networks, there are several issues with throughput, power consumption, and traffic congestion that have a detrimental effect on network performance. With parallel queues in the input buffer, this research presents the VIP-based VC router, a virtual channel router technique that improves system performance, reduces power consumption, and resolves deadlocks. Eight-, sixteen-, and thirty-two-bit systems can all use the suggested method. The Booksim simulator was used to conduct the simulation and evaluate the suggested routing method on a range of workloads. When compared to the wormhole router architecture, the experimental findings show improved system performance in terms of low power consumption and high throughput. Raghava Rao et al. [5], many products that are network overhead appear to have been created with IoT devices. We need to take into account things like dependability, low energy usage, etc. Finding answers to problems with scalability, reliability, network optimization, and quality of service (QoS) is essential to the advancement of IoT. The suggested method took into account a heterogeneous network that uses less electricity and has a long lifespan and good throughput. It is necessary to provide specifications for areas, nodes, sink locations, and data aggregation. This method's cluster head selection takes into account throughput, data communication rate, live node analysis, and a decrease in node energy consumption. However, developing an embedded Internet of Things system is challenging. For autonomous cellular networks, we looked at the ADEEC technique, which enhances network resilience and performance. Compared to existing methods, it is possible to convey messages more successfully in varied environments. Comparing the experimental findings of the proposed ADEEC to LEACH, MODLEACH, and DEEC, the throughput is outperformed by 19%,

An International Open Access, Peer-Reviewed Refereed Journal Impact Factor: 6.4 Website: <a href="https://ijarmt.com">https://ijarmt.com</a> ISSN No.: 3048-9458

16.5%, and 9.6%, respectively. When compared to LEACH, MODLEACH, and DEEC approaches, the network life span of ADEEC is 18%, 17%, and 13% longer, respectively.

G. Shanthi et al. [6], Cascaded integrated comb (CIC) filters are typically used as down samplers for sigma-delta modulators. This filter is typically used in audio applications where it helps to increase the signal-to-noise ratio and the resolution of the audio signal being transferred from the transmitter end. The CIC filter outperforms other filters in terms of noise cancellation and can be used in their stead. In this research, we introduced a CIC filter that transmits audio signals and allows for highly efficient decoding of such signals. The filter is first constructed in Matlab using the Simulink toolbox for FPGA implementation. Next, the HDL Coder library in MATLAB is used to extract the Verilog file for the Simulink implementation of the CIC filter. The Verilog file is then transferred to the FPGA for examination. Lastly, as compared to the current approach, the outcomes from the suggested CIC filter include higher gain, greater resolution, and fewer LUTs.

Sai Kumar et al. [7], multiplication are one of the main functions of a digital signal processing system. The total performance of the DSP system is impacted by the multiplier's performance. Therefore, designing a multiplier implementation that is both efficient and fast is essential. Complex calculations can be made simpler to complete orally by using Vedic mathematics. In Vedic mathematics, the multiplication algorithm is called Urdhva Triyambakam. In this study, we use the Brent Kung adder to improve the performance of the Vedic multiplier. Since the Urdhva Tiryagbhyam sutra creates the least amount of latency and applies to all instances of algorithms for N x N bit integers, it is being adopted in place of alternative multiplication schemes. An 8-bit vedic multiplier is constructed with four 4-bit vedic multipliers, two 8-bit Brent Kung adders, one 4-bit Brent Kung adder, and an OR gate. Similarly, two 4-bit Brent Kung Adders, one 2-bit Brent Kung Adder, one OR gate, and four 2-bit vedic multipliers are combined to generate a 4-bit vedic multiplier. An eight-bit vedic multiplier is then created by combining these four-bit vedic multipliers. The 8 x 8 Vedic Multiplier was then programmed in Verilog HDL and simulated and synthesized using Xilinx Vivado Software. When compared to related works, the speed performance of the suggested Vedic Multiplier is superior.

**Sayed et al. [8],** the FIR filter of the 45nm technical node, a fundamental filter in DSP applications, has been introduced in this research. In order to enhance the circuit is cost and power consumption, hybrid adders have been introduced. The suggested FIR filter additionally incorporates a D-type register and a Vedic multiplier. For the purpose of comparing

An International Open Access, Peer-Reviewed Refereed Journal Impact Factor: 6.4 Website: <a href="https://ijarmt.com">https://ijarmt.com</a> ISSN No.: 3048-9458

computational data, the 2-bit 4 tap direct and transposed forms of the FIR filter were created. The hybrid adder concept uses nearly six times less power than our conventional adder that uses complementary CMOS logic, according to the results. Power consumption, area, and transistor counts are further decreased by the direct-from FIR's fewer delay elements. Consequently, our circuits have greatly increased the FIR filter's overall performance and power consumption. Microwind was used to develop the layout, while DSCH software was used to implement the circuits.

### **TYPES OF MULTIPLIER**

These are the conventional multipliers having regular structures. Add and shift algorithm is used for its operation and hence its circuit is based on this algorithm. By direct mapping of the manual multiplication into hardware, an Array multiplier circuit can be developed [8]. An array of adder circuits can be used to accumulate partial products. The partial products are generated by multiplying the multiplicand with each bit of multiplier. The bit order decides the amount of shift of partial products. At the final stage, the partial products are added. The number of generated partial products is equal to that of multiplier bits. If multiplier length is equal to N, then N-1 numbers of adders are required to implement array multiplier [9].

### **Vedic Multiplier**

Vedic Mathematics is an ancient system of mathematics existed in India. In this eminent approach, methods of basic arithmetic are simple, powerful and logical. Another advantage is its regularity. These advantages make Vedic Mathematics an important topic for research. Vedic Mathematics rules are mainly based on sixteen Sutras. Out of these sixteen Sutra's Urdhva Triyakbhyam sutras and Nikhilam sutras are used for multiplication. Vedic multipliers are considered to be the best compared with conventional multipliers and Urdhva Triyakbhyam Sutra based multiplication is more efficient compared to that of Nikhilam Sutra [10]. Implementation of Vedic mathematics on FPGA is easy due to its regularity and simplicity [4]. All partial products required for multiplication are calculated much before actual multiplication begins. This is the big advantage of this multiplication. Based on the Vedic Mathematics algorithm, these partial products are added to obtain final product which leads to a very high speed approach. Multiplier designs based on Vedic mathematics are with high speed and consume relatively low power. Multipliers are the basic and key blocks of a Digital Signal processor. Multiplication is the key process in improving the computational speed of Digital Signal Processors [6]. Convolution, Fast Fourier transforms and various other transforms make

An International Open Access, Peer-Reviewed Refereed Journal Impact Factor: 6.4 Website: <a href="https://ijarmt.com">https://ijarmt.com</a> ISSN No.: 3048-9458

use of multiplier blocks [11]. Among various methods of multiplications in Vedic mathematics, Urdhva Tiryagbhyam is efficient. Urdhva Tiryagbhyam is a general multiplication formula applicable to all cases of multiplication.

### **Booth Series of Multipliers**

There is no need to take the sign of the number into deliberation in dealing with unsigned multiplication. However in signed multiplication the process will be changed because the signed number is in a 2's compliment pattern which would give a wrong result if multiplied by using similar process for unsigned multiplication [6]. Booth's algorithm is used for this. Booth's algorithm preserves the sign of the result. Booth multiplication allows for smaller, faster multiplication circuits through encoding the signed numbers to 2's complement, which is also a standard technique used in chip design, [6] and provides significant improvements by reducing the number of partial product to half over "long multiplication" techniques. Radix 2 is the conventional booth multiplier.

### Radix 2

In booth multiplication, partial product generation is done based on recoding scheme e.g. radix 2 encoding. Bits of multiplicand (Y) are grouped from left to right and corresponding operation on multiplier (X) is done in order to generate the partial product [19]. In radix-2 booth multiplication partial product generation is done based on encoding which is as given by Table 1. Parallel Recoding scheme used in radix-2 booth multiplier is shown in the Table 1.

Table 1: Booth recoding for radix 2

| Qn | $Q_{n+1}$ | Recoded Booth | Operation           |

|----|-----------|---------------|---------------------|

| 0  | 0         | 0             | Shift               |

| 0  | 1         | +1            | Add x<br>Subtract x |

| 1  | 0         | -1            |                     |

| 1  | 1         | 0             | Shift               |

### Radix 4

One of the solutions attaining high speed multipliers is to improve parallelism. It helps in decreasing the number of consecutive calculation stages [1]. The Original version of Booth's multiplier (Radix - 2) had two drawbacks [7]. The number of Add or Subtract operations became variable and hence became difficult while designing Parallel multipliers. The Algorithm becomes disorganized when there are isolated 1s. These problems are overthrown

An International Open Access, Peer-Reviewed Refereed Journal Impact Factor: 6.4 Website: <a href="https://ijarmt.com">https://ijarmt.com</a> ISSN No.: 3048-9458

by using Radix 4 Booth's algorithm which can browse strings of three bits with the algorithm. The above recoding has the nice feature that they translate into the partial products shown in table 2.

| Multiplier Bits<br>Block |     | Recoded 1-bit<br>pair |     | 2-bit booth |                  |                 |

|--------------------------|-----|-----------------------|-----|-------------|------------------|-----------------|

| i+1                      | - 1 | i-1                   | i+1 | - 1         | Multiplier Value | Partial Product |

| 0                        | 0   | 0                     | 0   | 0           | 0                | Mx0             |

| 0                        | 0   | 1                     | 0   | 1           | 1                | Mx1             |

| 0                        | 1   | 0                     | 1   | -1          | 1                | Mx1             |

| 0                        | 1   | 0                     | 1   | 0           | 2                | Mx2             |

| 1                        | 0   | 0                     | -1  | 0           | -2               | Mx-2            |

| 1                        | 0   | 1                     | -1  | 1           | -1               | Mx-1            |

| 1                        | 1   | 0                     | 0   | -1          | -1               | Mx-1            |

| 1                        | 1   | 0                     | 0   | 0           | 0                | Mx0             |

Table 2: Booth recoding for radix 4

### **DIFFERENT TYPES OF ADDER**

#### Parallel Adder:-

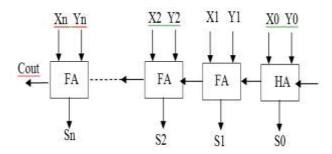

Parallel adder can add all bits in parallel manner i.e. simultaneously hence increased the addition speed. In this adder multiple full adders are used to add the two corresponding bits of two binary numbers and carry bit of the previous adder. It produces sum bits and carry bit for the next stage adder. In this adder multiple carry produced by multiple adders are rippled, i.e. carry bit produced from an adder works as one of the input for the adder in its succeeding stage. Hence sometimes it is also known as Ripple Carry Adder (RCA). Generalized diagram of parallel adder is shown in figure 1.

Figure 1: Parallel Adder

An n-bit parallel adder has one half adder and n-1 full adders if the last carry bit required. But in 754 multiplier's exponent adder, last carry out does not required so we can use XOR Gate instead of using the last full adder. It not only reduces the area occupied by the circuit but also

An International Open Access, Peer-Reviewed Refereed Journal Impact Factor: 6.4 Website: <a href="https://ijarmt.com">https://ijarmt.com</a> ISSN No.: 3048-9458

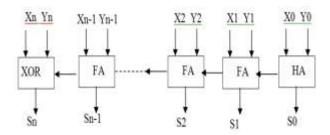

reduces the delay involved in calculation. For SPFP and DPFP multiplier's exponent adder, here we Simulate 8 bit and 11 bit parallel adders respectively as show in figure 2.

Figure 2: Modified Parallel Adder

### Carry Skip Adder:-

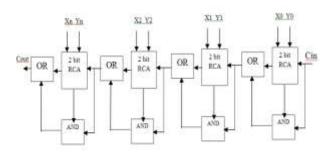

This adder gives the advantage of less delay over Ripple carry adder. It uses the logic of carry skip, i.e. any desired carry can skip any number of adder stages. Here carry skip logic circuitry uses two gates namely "and gate" and "or gate". Due to this fact that carry need not to ripple through each stage. It gives improved delay parameter. It is also known as Carry bypass adder. Generalized figure of Carry Skip Adder is shown in figure 3.

Figure 3: Carry Skip Adder

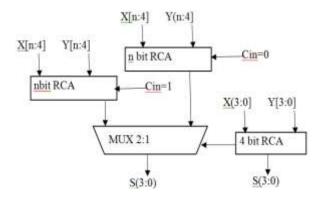

### Carry Select Adder:-

Carry select adder uses multiplexer along with RCAs in which the carry is used as a select input to choose the correct output sum bits as well as carry bit. Due to this, it is called Carry select adder. In this adder two RCAs are used to calculate the sum bits simultaneously for the same bits assuming two different carry inputs i.e. '1' and '0'. It is the responsibility of multiplexer to choose correct output bits out of the two, once the correct carry input is known to it. Multiplexer delay is included in this adder. Generalized figure of Carry select adder is shown in figure 4. Adders are the basic building blocks of most of the ALUs (Arithmetic logic units) used in Digital signal processing and various other applications. Many types of adders are

An International Open Access, Peer-Reviewed Refereed Journal Impact Factor: 6.4 Website: <a href="https://ijarmt.com">https://ijarmt.com</a> ISSN No.: 3048-9458

available in today's scenario and many more are developing day by day. Half adder and Full adder are the two basic types of adders. Almost all other adders are made with the different arrangements of these two basic adders only. Half adder is used to add two bits and produce sum and carry bits whereas full adder can add three bits simultaneously and produces sum and carry bits.

Figure 4: Carry Select Adder

### **CONCLUSION**

This study presented a comparative analysis of Finite Impulse Response (FIR) filter implementations using various multipliers and adders to evaluate their impact on the overall performance of digital filter architecture. FIR filters, known for their stability and linear phase characteristics, are computationally intensive, making the choice of arithmetic components—particularly multipliers and adders—critical in achieving optimized performance. The investigation included Booth, Wallace Tree, and Vedic multipliers, along with Ripple Carry Adder (RCA), Carry Look-Ahead Adder (CLA), and Carry Save Adder (CSA).

Simulation results demonstrated that the Vedic multiplier, when combined with the CSA or CLA, offered the most efficient trade-off between speed, area, and power consumption. Wallace Tree multipliers provided superior speed but consumed more hardware resources, while Booth multipliers showed moderate performance with higher delays. The study highlights that an optimized combination of Vedic multiplier and CSA yields the best results for low-power and high-speed FIR filter applications.

Overall, the findings emphasize the importance of architectural selection in digital filter design, particularly for VLSI and FPGA-based systems. This analysis can serve as a reference for hardware designers aiming to implement efficient FIR filters in real-time DSP applications such as communication systems, biomedical signal processing, and audio processing devices.

An International Open Access, Peer-Reviewed Refereed Journal Impact Factor: 6.4 Website: <a href="https://ijarmt.com">https://ijarmt.com</a> ISSN No.: 3048-9458

#### **REFERENCES**

- [1] K. Sravani, M. Saisri, U. Vidya Sivani and A.Ramesh Kumar, "Design and Implementation of Optimized FIR Filter using CSA and Booth Multiplier for High Speed Signal Processing", 4th International Conference for Emerging Technology (INCET), IEEE 2023.

- [2] A. S. Kumar et al., "An Efficient AVR interfaced Bluetooth controlled Robotic Car system," 2023 13th International Conference on Cloud Computing, Data Science & Engineering (Confluence), India, pp. 499-502, 2023.

- [3] A. S. Kumar et al., "A Novel RRAM-based FPGA architecture with Improved Performance and Optimization Parameters," 2022 IEEE 19th India Council International Conference (INDICON), Kochi, India, pp. 1-5, 2022.

- [4] B. N. K. Reddy and A. S. Kumar, "An Efficient Low-Power VIP based VC Router Architecture for Mesh-based NoC," 2022 IEEE 19th India Council International Conference (INDICON), India, pp. 1-5, 2022.

- [5] Raghava Rao, K., Naresh Kumar Reddy, B. & Kumar, A.S. "Using advanced distributed energy efficient clustering increasing the network lifetime in wireless sensor networks", Soft Computing, 2023.

- [6] G. Shanthi, A. S. Kumar, et al., "An Efficient FPGA Implementation of Cascade Integrator Comb Filter," 2022 International Conference on Intelligent Innovations in Engineering and Technology (ICIIET), pp. 151-156, 2022.

- [7] Sai Kumar, U. Siddhesh, N. Sai kiran and K. Bhavitha, "Design of High Speed 8-bit Vedic Multiplier using Brent Kung Adders," 2022 13th International Conference on Computing Communication and Networking Technologies (ICCCNT), pp. 1-5, 2022.

- [8] Sayed, J. F., Hasan, B. H., Muntasir, B., Hasan, M., & Arifin, F. (2021). "Design and Evaluation of a FIR Filter Using Hybrid Adders and Vedic Multipliers". 2021 2nd International Conference on Robotics, Electrical and Signal Processing Techniques (ICREST).

- [9] S. China Venkateshwarlu, Mohammad, Chandra Shaker Pittala and Rajeev Ratna Vallabhuni, "Optimized Design of Power Efficient FIR Filter Using Modified Booth Multiplier", 4th International Conference on Recent Trends in Computer Science and Technology, IEEE 2021.

An International Open Access, Peer-Reviewed Refereed Journal Impact Factor: 6.4 Website: <a href="https://ijarmt.com">https://ijarmt.com</a> ISSN No.: 3048-9458

- [10] Ghasemi, Mir Majid, Amir Fathi, Morteza Mousazadeh, and Abdollah Khoei, "A new high speed and low power decoder/encoder for Radix-4 Booth multiplier," International Journal of Circuit Theory and Applications, 2021.

- [11] Chang, Yen-Jen, Yu-Cheng Cheng, Shao-Chi Liao, and Chun-Huo Hsiao, "A Low Power Radix-4 Booth Multiplier with Pre-Encoded Mechanism," IEEE Access 8, 2020.

- [12] Akshitha V. Ramesh et al. "Implementation and Design of FIR Filters using Verilog HDL and FPGA" Perspectives in Communication Embedded-systems and Signal-processing-PiCES vol. 4.5 pp. 85-88, 2020.

- [13] Ranjeeta Yadav Rohit Tripathi and Sachin Yadav "FPGA Implementation of Efficient FIR Filter" International Journal of Engineering and Advanced Technology (IJEAT) vol. 9, no. 3 February 2020.

- [14] Zhang, Tingting, Weiqiang Liu, Jie Han, and Fabrizio Lombardi, "Design and Analysis of Majority Logic Based Approximate Radix-4 Booth Encoders," In IEEE/ACM International Symposium on Nanoscale Architectures (NANOARCH), pp. 1-6. IEEE, 2019.

- [15] Gharabaghlo, Nader Sharifi, and Tohid Moradi Khaneshan, "Performance Analysis of High Speed Radix-4 Booth Encoders in CMOS Technology," Majlesi Journal of Electrical Engineering 13, no. 3, 49-57, 2019.

- [16] Madugula Sumalatha Panchala Venkata Naganjaneyulu and K. Satya Prasad "Low power and low area VLSI implementation of vedic design FIR filter for ECG signal de-noising" Microprocessors and Microsystems vol. 71 pp. 102883, 2019.

- [17] Oguzhan COSKUN and A. V. C. I. Kemal "FPGA Schematic Implementations and Comparison of FIR Digital Filter Structures" Balkan Journal of Electrical and Computer Engineering vol. 6.1 pp. 20-28, 2018.